[本站讯]4月9日,全国集成电路标准化技术委员会(SAC/TC599)RISC-V工作组(WG7)工作会议在湖北武汉举行。智研院戴鸿君教授作为高校专家代表参会,与产学研用各界代表共同发布国内首款RISC-V全栈测评工具。

会议聚焦我国深度参与RISC-V国际组织总体情况、RISC-V开放计算底座与普惠AI时代建设、面向具身智能与人形机器人的RISC-V芯片实现路径等前沿方向和核心议题,明确了下一阶段RISC-V领域标准化建设的重点推进方向,为集成电路产业高水平科技自立自强和新型工业化提供坚实底座。

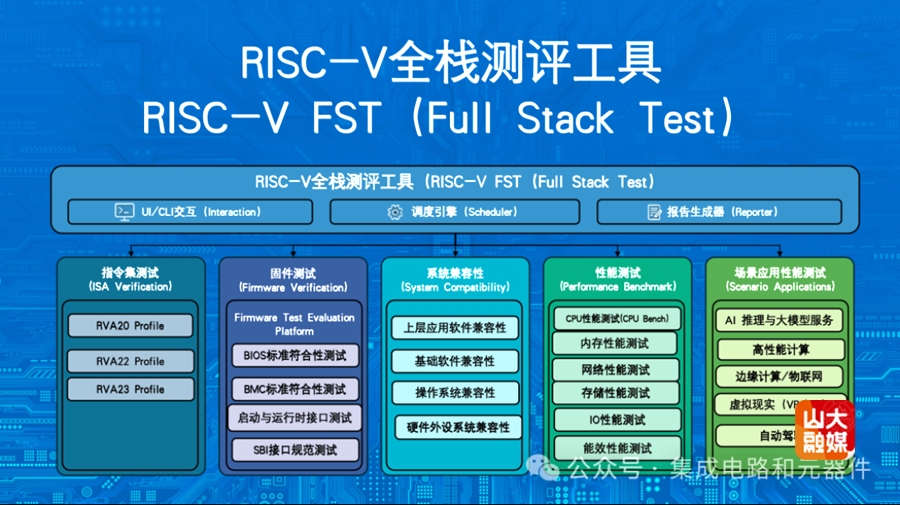

本次联合发布的RISC-V全栈测评工具由中国电子技术标准化研究院牵头,联合山东大学、中国科学院软件所、阿里达摩院、进迭时空、超睿科技等国内顶尖科研院所与龙头企业共同研制,是我国首款自研 RISC-V 全栈测评工具(RISC-V FST)。该工具全面覆盖指令集、固件、系统兼容、性能与典型应用场景,为产业提供一站式、全流程、权威可信的合规验证能力,填补了我国RISC-V全链路标准化测评的空白,为RISC-V芯片在服务器、智能终端、汽车电子等关键领域的规模化部署筑牢质量防线,标志着我国在RISC-V标准化测评领域取得突破性进展,引发与会嘉宾高度关注和热烈反响。

该工具的发布,是我国 RISC-V产业产学研用协同创新的重要成果,充分体现了行业聚力共建标准、共筑生态、共谋发展的强大合力。这一里程碑事件深刻表明,国产 RISC-V产业生态已从单点技术突破,全面迈向全链协同、标准引领、生态共筑的全新发展阶段,为推动我国集成电路产业高水平科技自立自强、构建开放兼容安全可控的计算架构体系注入强劲动力。

本次会议由全国集成电路标准化技术委员会主办。北京开芯研究院工作组副组长唐丹院长主持会议,工业和信息化部电子信息司相关处室负责人、秘书处单位代表,科研院所、龙头企业及生态伙伴代表近100人参加会议。