[本站讯]近日,山东大学体系结构与嵌入式系统研究中心在电子设计自动化与计算机系统领域取得重要突破,三项成果被电子设计自动化领域顶级学术会议DAC (Design Automation Conference) 2026录用,充分显示了山东大学在体系结构和电子设计自动化领域的持续创新能力与国际学术影响力,获得了国际学术界的广泛认可。

成果一:ReflectBench: An Agentic Framework for Generating System-Level Design Testbench via Consensus and Reflection(大语言模型辅助硬件设计验证,促进国产芯片设计生态发展)

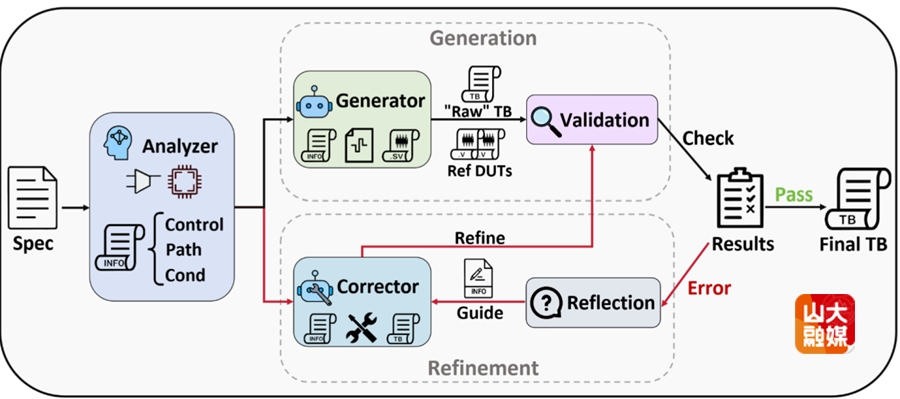

图1:ReflectBench流程图

该研究面向大语言模型辅助的芯片设计流程,伴随着基于大语言模型生成的大量硬件设计,其正确性验证对于确保电子设计的功能正确性至关重要。针对基于大语言模型生成的硬件电路设计“测试难”的问题,研究提出了一套基于共识和反思机制的人工智能体(AI Agent)硬件测试系统ReflectBench,该智能体框架具备逻辑分析、共识验证、反馈自省与测试平台自修正能力,可运行自动化系统级硬件设计验证。为进一步减少数据准备的人工投入,该工作还设计了基于自反馈机制的知识挖掘方法,可自动构建符合硬件语义的高效检索硬件设计语义库。此外,该工作开发了包含53个系统级硬件设计基准测试集,及评估验证框架。该项工作对于促进我国硬件设计,特别是芯片设计行业的发展具有一定的意义。

论文第一作者为山东大学计算机学院硕士研究生刘俊喆,通讯作者为贾振格教授,合作者包括山东大学申兆岩教授、赵梦莹教授、本科生张谱原、王劲恒,浙江大学严哲雨教授,德国慕尼黑工业大学赵卓睿博士,浪潮云李超、陈孝委研究员。

成果二:Knowledge-Driven Hybrid SSD Management Enhanced by Fine-Tuned LLMs(知识驱动的混合闪存固态盘管理优化,提升智能存储系统性能与效率)

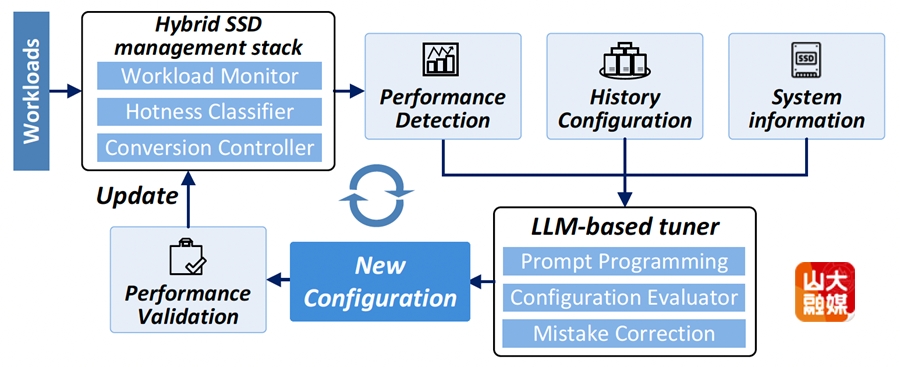

图2:所提方案系统流程图

该研究面向混合闪存固态盘中管理策略复杂、参数空间庞大、传统优化方法依赖专家经验且难以动态适应负载变化等问题,创新性地提出了一种知识驱动优化框架。其核心思想是:不直接用大语言模型替代现有混合闪存固态盘管理模块,而是将混合闪存固态盘的数据放置、模式转换、垃圾回收等协同控制问题转化为参数调优问题,利用专用微调大语言模型的知识理解与推理能力,为系统生成更优的运行配置,从而实现对混合闪存固态盘性能与写放大的联合优化。实验结果表明,所提出的方案在多种真实工作负载下均表现出显著优势。

论文第一作者为山东大学计算机学院博士生魏倩,通讯作者为申兆岩教授,合作者包括山东大学博士生陈泽豪、周天任,得克萨斯大学达拉斯分校李炳哲老师和博士生李轶。

成果三:Enabling Robust On-Device Personalization via Pulse-Based Mapping and Noise Suppression for Non-Ideal CIM Architecture(面向存算一体架构的微调计算框架,赋能端侧智能进化)

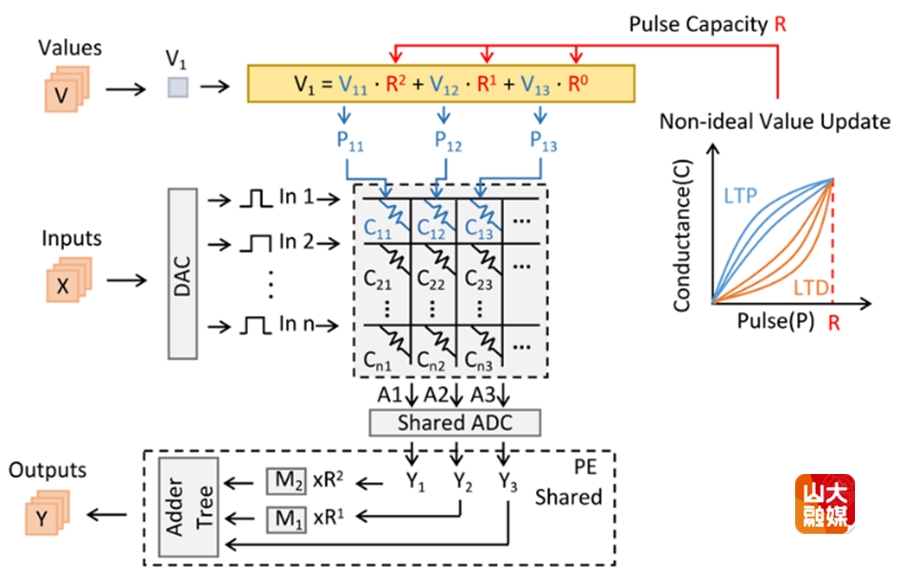

图3:权重更新时电脉冲映射方案

该研究针对存算一体(CIM)架构在边缘侧 AI 应用中面临的瓶颈:ReRAM 等器件存在非线性电导响应和随机噪声等非理想特性,导致深度学习模型难以直接在片上进行微调计算从而完成本地适配。为此,该研究提出了一套片上高效抗噪微调框架CIM-MP,包括权重更新时电脉冲映射方案以及去噪方案,使存算架构在抗噪推理的基础上,具备了运行抗噪且高效的片上微调能力。CIM-MP首先提出基于脉冲的多单元映射策略,通过将单一逻辑权重高效映射至多个存储单元,缓解了梯度值与硬件脉冲步长之间失配问题;设计特征变异消除机制,抑制前向传播中由硬件非理想特性引入的特征图模拟噪声;CIM-MP采用梯度自适应净化机制,利用贝叶斯后验推理将结构化的硬件噪声从梯度信号中分离,确保更新方向的有效性。实验结果表明,相较于现有面向存算架构的抗噪方法,CIM-MP使模型本地微调精度最高提升35.1%,相较于传统计算方案,能耗降低46–50倍。

论文第一作者为山东大学计算机学院硕士研究生石奕扬,通讯作者为贾振格教授和北京大学深圳研究生院王少聪研究员,合作者包括山东大学计算机学院本科生刘昕煜。

DAC (Design Automation Conference),全称国际设计自动化会议, 是中国计算机学会(CCF)推荐的A类会议,由美国计算机协会(ACM)和电气与电子工程师协会(IEEE)联合主办,始于1964年,拥有超过60年的历史,是全球芯片设计与自动化领域规模宏大、影响深远、历史悠久的顶级会议之一。